身为资深电子工程师,准确理解DDR3布线问题具有极高重要性。DDR3作为主流内存类型,已广泛运用于现今计算机体系。因此,精细的布线设计对提升DDR3内存模块的运行效率与稳定可靠不可或缺。接下来,简要阐述详解DDR3布线问题的关键核心。

什么是DDR3内存?

接下来,我们简明扼要地了解下DDR3内存。DDR3即'double data rate 3',为一类新型内存,凭借其较高的工作频次与带宽,已成为当前电脑、服务及其它各类计算机设备中必不可少的组件之一,能够极速提升数据传输速率并改善整体性能。

在实践运用领域,合理的DDR3排线设计,能充分拓展其性能潜力,同时有效规避信号干扰和时序偏移等常见问题。以下,我们将对DDR3布线设计中关键议题进行详细剖析。

如何选择合适的PCB材料?

PCB材料作为影响DDR3布线质量的关键要素之一,确保选择合适的PCB材料以保证信号传输的高质量至关重要。常用的PCB材料有FR-4和高频材料等种类,它们各自具备独特的介电常数与损耗因子特性,进而对信号传输产生作用。

挑选PCB材料需全方位考虑成本、性能需求及板厚等元素。依据实际情况精心筛选,适宜之选可有效缩减信号传输损失、减少信号反射,以提升整体系统效能。

如何进行差分对?

在DDR3布线上,差分对策略尤为关键。其通过两根正负导电线共同传送信息,以差异模式有效抵御内外干扰与噪音,从而增强信号完整性。

在构建差分对电路时,应确保两根传输线的长度及其阻抗完全相同,并竭力减少各方面的记忆效应与噪声损害。精心构建的差分对架构能显著增强信号品质、降低能耗,从而增强整个系统的稳健性。

如何避免串扰问题?

在DDR3布线设计过程中,串扰是一个普遍存在且相对严重的问题。由于信号线间隔过窄或干扰源信号强度过高,都会导致串扰现象,从而显著削弱信号传输质量。

为防止串扰引发的质量问题,在DDR3线路布局中,可采纳诸如增大地表间距、加装屏蔽装置以及优化信号路径等策略,以削减此类干扰的消极影响。高效控制串扰将助力提升系统抗干扰能力、降低错误码率,保证系统稳定运作。

时序匹配如何实现?

时序匹配乃DDR3布线设计至关重要环节。在信息传送过程,各信号通道需严守时序规范,确保数据能准确读取与存储。

为确保时序匹配的准确性,需重点关注各信号路径的长度一致性、延时调控以及时钟同步等要素。在精良调整信号路径长度及采用适当的延迟补偿技巧后,方可实现时序匹配的严谨要求,进而使系统品质及安全性得到提升。

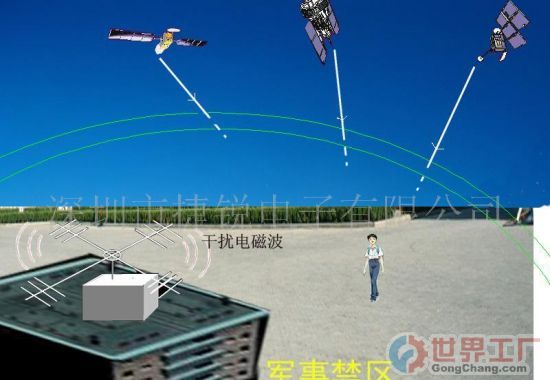

如何进行电磁兼容设计?

DDR3布线设计时,必须着重考量电磁兼容性的问题。高速信号的传输易引发强烈的电磁辐射及敏感度,因此在设计阶段必需采用相应方法减少电磁干扰,增强系统的抗干扰能力。

为了打造优良的电磁兼容性设计,必须在设计初期就全面考虑地域分布、屏蔽设施及接地体系等要素。通过精心制定的电源兼容设计策略,结合制作阶段严格遵守有关规定,能显著降低电磁干扰所带来的负面影响。

如何优化供电系统?

供电系统乃是影响DDR3内存模块性能与稳定性的至关重要因素之一。在布线设计过程中,应确保供电系统能持续而稳定地为内存模块供应能源,且达至其能耗需求。

针对电力供应的优化问题,我们建议在印刷电路板(PCB)设计起步阶段就充分考虑供电网络的布局、滤波器的选择与配置以及功率引脚的接入形式等要素。明确且完备的供电系统组织规划是确保其符合内存模块运行要求的关键,也将直接影响到我们最终使用的系统的稳定性和抗干扰能力。