同步动态随机存取存储器(SDRAM)被誉为一款高速的内存片,而DDR的地址线必须设计为同等长度,以确保数据传输的稳定性与可靠性。究竟应如何精准设计DDR地址线长度?以下是部分实用的建议供您参考。

1.了解DDR的工作原理

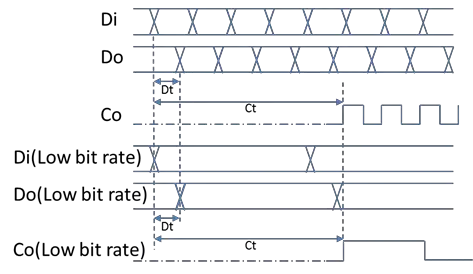

在深入探讨这一问题之前,我们必须首先掌握DDR内存工作机制。其在读写过程中预先分离,皆通过地址线标识读取与写入的具体位置。换言之,地址线的长度直接影响数据传输精确度。

2.确定等长原则

设计DDR地址线时应遵守等长原则,即所有地址线须长度统一,保证信号同步抵达目标定位区。

3.考虑布线规则

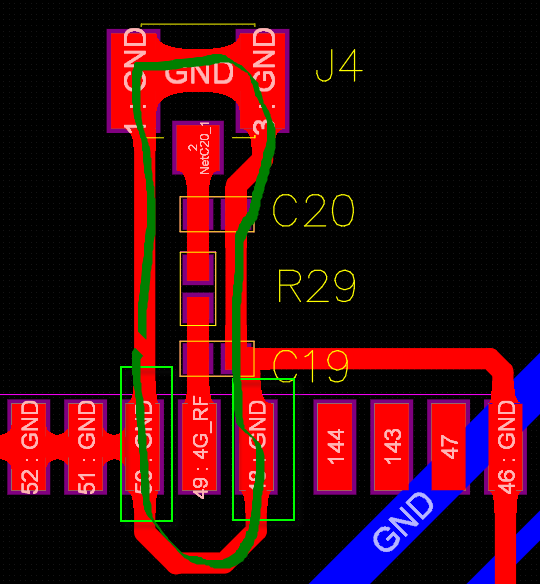

实际布局需遵循布线规律,依据此,适当调整PCB层级、走线规格以及间距等指标以确保等效长度需求得以实现。

4.使用仿真工具验证

为保证DDR地址线等长性能,构建完毕后运用仿真仪器进行精确检测。仿真可模拟各类运行环境以确认信号的传输速度与误差状况。

5.注意电磁兼容性

在设计DDR地址信号的布设中,需关注电磁兼容性的要求。由于地址信号易受外界干扰,我们需采用一系列抗干扰措施,如增加接地线路及加装屏蔽层等。

6.优化布局

为确保地址线等长性,可对布局进行最佳设计,有效缩短走线长度和减少潜在的交叉现象,同时也需要对PCB层次结构进行适当调整,以此降低信号传输不良带来的延迟风险。

7.及时调整

在实际制造过程中若发现DDR地址线长度差异过大,务必立即进行调整。可通过更改PCB布板或重新规划信号线路来解决此差异问题。

运用上述七种方法与策略,能够有效提升DDR地址线的设计质量,保证其等长特性。这有助于提升DDR内存的稳定度及可靠性,确保数据传输的精确性。期待本文能为各位提供宝贵参考!